## Parallel-Bridge Resonance-Type Fault Current Limiter

<sup>1</sup> K. Devi Annapurna, <sup>2</sup> J. Thanuj Kumar

Abstract - This paper proposes a new parallel-LC-reson ance-type fault current limiter (FCL) that uses a resistor in series with a capacitor and therefore, it can simulate load impedance during fault. By this way, The proposed FCL is capable of limiting the fault current magnitude near to the prefault magnitude of distribution feeder current by placing the resistor in the structure of the FCL. The voltage of the point of common coupling does not experience considerable sag during the fault In comparison with the previously this FCL does not use asuper conducting inductor in the resonant circuit, due to high cost the overall operation of the mentioned FCL in normal and fault conditions has been studied in detail. Also, the simulation and experimental results have found.

Keywords - Fault Current Limiter (FCL), Parallel Resonance, Resistor.

#### 1. Introduction

Rowth of power systems and their interconnections has resulted in increasing the short-circuit current level. The most common ways to limit high-level fault currents are upgrading switchgear and other equipment, splitting the power grid, using higher voltage connections (ac or dc), using highimpedance transformers, etc. These alternatives may create other problems such as loss of power system safety, reliability, high cost, and more power losses [1]–[4]. Fault current limiters (FCLs) are developed to overcome the aforementioned problems. An ideal FCL should have the following characteristics [5], [6]:

- 1) zero impedance in the normal operation;

- 2) no power loss in the normal operation;

- 3) large impedance in the fault conditions;

- 4) quick appearance of impedance when a fault occurs;

- 5) fast recovery after fault removal.

The implementation of FCLs in electric power systems is not restricted to suppressing the amplitudes of short-circuit currents. They are also utilized to variety of performances such as power quality improvement, power system transient stability enhancement, reliability improvement, and increasing transfer capacity of system electrical energy. Therefore, an ideal FCL should have another important characteristic in addition to the listed characteristics. It should play the load impedance role and be equal to the load impedance during fault to better operation in such performances [7]-[11]. Different topologies for the FCL are introduced in literatures such as superconducting FCLs (SFCLs), solid-state FCLs, fluxlock-type FCLs, and resonance-type SFCLs [12]-[19]. Resonance-type FCLs limit the fault current by using various topologies of series or parallel *LC* resonant circuits [18]-[23]. Series-resonance-type FCLs are composed of a series connection of a capacitor and a superconducting inductor. They do not allow the short-circuit current to increase instantaneously as the fault occurs. However, these FCLs cannot limit the fault current level if the fault continues. Thus, the fault current will increase continually [18], [19]. Because of the use of a superconducting inductor, some of these structures need high construction

Therefore, they are not commercially available, particularly for third-world countries. On the other hand, resonance-type FCLs, which do not use a superconducting inductor and replace it with an ordinary copper coil, make power losses in their structures [20], [21]. Previously introduced parallel-resonance-type FCLs have used two antiparallel semiconductor switches to make resonance condition between *L* and *C*. Operation of such structures results in large oscillations on the line current caused by *LC* resonance at first moments of the fault. These oscillations may harm system equipment [22], [23]. In this paper, a new structure for a parallel-*LC*-resonancetype FCL is introduced. The proposed FCL uses a resistor in series with a capacitor, and therefore, it can simulate load impedance during fault. By this way, it can limit the fault

<sup>&</sup>lt;sup>1</sup> M.Tech Student, Lenora College of Engineering- Rampachodavaram

<sup>&</sup>lt;sup>2</sup> Asst. Professor, Lenora College of Engineering- Rampachodavaram

current level near to prefault condition. From the power quality point of view, by equating fault current and beforefault line current, the voltage of the point of common coupling (PCC) will not experience considerable change during fault condition, and power quality will improve. In comparison with the previously introduced resonance-type FCLs, this FCL does not use a superconducting inductor in the resonant circuit, and as a result, it is simpler to manufacture and has lower cost. Its inductor is bypassed because of small voltage drop on the diode bridge in the normal operation, and therefore, it has negligible power losses. On the other hand, by using the proposed FCL, the fault current will not increase continually, which happens in most of series-resonance-type FCLs. By using the resistor in this structure, the problem of line current oscillations in the fault condition is solved. Analytical analysis and design considerations for this FCL are presented, and matrix laboratory (MATLAB) software [24] is used to solve the resulted formulas. The circuit operation in the normal and fault conditions is simulated by using PSCAD/EMTDC software [25]. Experimental results in laboratory scale are presented too.

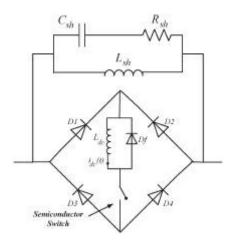

Fig. 1. Single-phase power circuit topology of the proposed parallel resonance- type FCL.

# 2. Power Circuit Topology and Principles of Operation

Fig. 1 shows the single-phase power circuit topology of the proposed FCL. It is necessary to use a similar circuit for each phase in a three-phase distribution system. This structure is composed of two main parts which are as follows.

1) Bridge part: This part consists of a rectifier bridge containing D1-D4 diodes, a small dc-limiting reactor (Ldc), a self-turnoff semiconductor switch (such as a gate turnoff thyristor and an insulated-gate bipolar transistor) and its snubber circuit, and a freewheeling diode (Df).

2) Resonance part: This part consists of a parallel *LC* resonance circuit (*L*sh and *C*sh) (its resonant frequency is equal to power system frequency) and a resistor *R*sh in series with the capacitor.

The bridge part of the proposed FCL operates as a high-speed switch that changes the fault current path to the resonance part when the fault occurs. Obviously, it is possible to substitute this part with an antiparallel connection of two self-turnoff semiconductor switches [22], [23]. Using a diode rectifier bridge has two advantages compared to two antiparallel switches as follows.

- 1) This structure uses only one controllable semiconductor switch which operates in the dc side instead of two switches that operate in the ac side. The control circuit is simpler because of no need for ON/OFF switching in the normal operation case.

- 2) It is possible to use a small reactor in series with the semiconductor switch at the dc side. This reactor plays two roles as follows.

- a) It is snubber for a semiconductor switch.

- b) It is as a current limiter at first moments of fault occurrence.

However, placing the dc reactor inside the bridge makes the voltage drop on it because of dc current ripple. However, the current ripple is low, and consequently, the voltage drop caused by it is not considerable in comparison with the feeder's voltage. Current ripple and voltage drop equations are studied completely in [6] and [26].

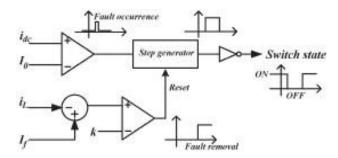

Fig. 2. Control circuit of the proposed FCL.

It is important to note that high-rating semiconductor switches are commercially available with current rating up to 24 kA and voltage rating up to 4 kV [27]. Also, it is possible to use some series and/or parallel self-turnoff switches considering high current and voltage levels. The semiconductor switch needs a suitable snubber circuit for its protection, which is not shown in Fig. 1 for simplicity.

Also, high-rating semiconductor switches, their protection procedure, and minimization of their power losses are discussed in [28]–[32].

From the power loss point of view, in the normal condition, the proposed FCL has the losses on the rectifier bridge diodes, the semiconductor switch, and the small resistance of the dc reactor. Each diode of the rectifier bridge is ON in half a cycle, while the semiconductor switch is always ON. Therefore, the power losses of this FCL in the normal operation can be calculated as

$$P_{loss} = P_R + P_D + P_{SW} = R_{dc}I_{dc}^2 + 4V_{DF}I_{ave.} + V_{SWF}I_{dc}$$

where

*I*dc- dc-side current which is equal to the peak of the line current (*I*peak);

*R*dc- resistance of the dc reactor;

VDF- forward voltage drop on each diode;

VSWF- forward voltage drop on the semiconductor switch:

*I*ave-. average current of the diodes in each cycle that is equal to Ipeak/ $\pi$ .

Considering (1) and the small value of the dc reactor in this structure, the total power losses of the proposed structure become a very small percentage of the feeder's transmitted power.

Fig. 2 shows the control circuit of the proposed FCL. In the normal operation of the power system, the semiconductor switch is ON. Therefore, *L*dc is charged to the peak of the line current and behaves as a short circuit. Using the semiconductor devices (the diodes and semiconductor switch) and the small dc reactor causes a negligible voltage drop on the FCL. When a fault occurs, the dc current becomes greater than the maximum permissible current *I*0, and the control circuit detects it and turns the semiconductor switch off. Therefore, the bridge retreats from utility. At this moment, the freewheeling diode *Df* turns on and provides free path for discharging the dc reactor.

When the bridge turns off, the fault current passes through the parallel resonance part of the FCL. Consequently, large impedance enters to the circuit and prevents the fault current from rising. In the fault condition, the parallel *LC* circuit starts to resonate. In this case, because of resonance, the line current oscillates with large magnitude [22], [23]. These oscillations may lead to damaging system equipment or putting them in stress. However, by placing a resistor (*R*sh) in series with the capacitor, current transients damp quickly that will be shown in Section V. In addition, by using *R*sh, the voltage drop on *R*sh causes

that the voltage across the capacitor is decreased during fault.

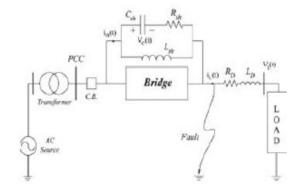

Fig. 3. Single-line diagram of the power system.

When the fault disappeared, while the semiconductor switch is OFF, the parallel part of the FCL will be connected in series with the load impedance. Therefore, the line current will be decreased instantaneously. To detect this instantaneous reduction of the line current, iL is compared with If that can be calculated from

$$I_f = \frac{|\overline{V}_{PCC}|}{|Z_{eq}|}$$

where Zeq is the equivalent impedance of the resonance part.

When the difference of iL and If becomes greater than k as the fault removal sign, the control circuit turns the semiconductor switch on. Therefore, the power system returns to the normal state. The value of k can be calculated from

$$k = \frac{|\overline{V}_{PCC}|}{|\overline{Z}_{eq}|} - \frac{|\overline{V}_{PCC}|}{|\overline{Z}_{eq} + \overline{Z}_{L,min}|}$$

(3)

where ZL, min is the minimum impedance of the load on the protected feeder.

As pointed, some of previously proposed FCL structures have ac power losses at the resonant circuit in the normal condition, because of placing a large inductor in the line current path [20], [21]. However, the proposed structure in this paper has very low losses in the normal condition, because the inductor is bypassed by the bridge part. Also, by choosing proper values for the resonant circuit, the proposed FCL limits the fault current in a way that the power system is not affected by the fault. In such

condition, there will not be any considerable voltage sag on the PCC voltage.

#### 3. Analytical Analysis

Fig. 3 shows the single-line diagram of the power system including the proposed FCL. This figure is composed of a power source, a transformer, a circuit breaker (C.B.), an FCL, a line impedance, and a load.

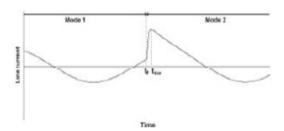

Fig. 4. Enlarged view of the line current before and after a fault.

The circuit breaker (C.B.) which is rated for the full system short-circuit current is placed to ensure the adequate protection of the power system during permanent faults. The utility voltage is a three-phase sinusoidal waveform. The utility-side impedance is modeled by a series connection of a resistor Rs and an inductor Ls. The analytical analysis is discussed in two modes as follows: Mode 1) prefault steady-state operation (until tf in Fig. 4); Mode 2) between fault occurrence and fault removal (from tf to fault removal time in Fig. 4).

#### A. Mode 1

In the normal operation of the power system, the bridge part bypasses the resonant circuit. In this condition, the line current (iL) can be expressed by the following differential equation:

$$V_s \sin(\omega t) = RiL + \omega L$$

dist

where

Vs peak of the utility voltage;  $\omega$  angular frequency of the utility voltage;

R = Rs + RL + RD resistance of the source side, load, and distribution feeder;

L = Ls + LL + LD inductance of the source side, load, and distribution feeder.

$$i_L(\omega t) = \left(\frac{V_s}{\sqrt{R^2 + \omega^2 L^2}}\right) \left[\left(\frac{L\omega}{\sqrt{R^2 + \omega^2 L^2}}\right) e^{-\left(\frac{R}{\omega L}\right)\omega t} + \sin(\omega t - \varphi)\right]$$

(5)

Therefore, the line current equation can be derived as follows:

Where

$$\varphi = \arctan\left(\frac{\omega L}{R}\right)$$

#### B. Mode 2

When a short circuit occurs, the dc-limiting reactor can limit the increasing rate of the fault current. The semiconductor switch does not operate until the line current reaches to a predefined value. By semiconductor switch operation in the *t*sw instant (Fig. 4), the bridge is switched off, and the fault current is suppressed by the resonant circuit. Therefore, the differential equation of the fault current can be expressed as follows:

$$L_s L_{sh} C_{sh} \left(\frac{d^3 i_L}{dt^3}\right)$$

+  $\left(R_s L_{sh} C_{sh} + L_s R_{sh} C_{sh} + R_{sh} L_{sh} C_{sh}\right) \left(\frac{d^2 i_L}{dt^2}\right)$

+  $\left(L_s + R_{sh} C_{sh} R_s + L_{sh}\right) \left(\frac{d i_L}{dt}\right) + R_s i_L$

=  $\left(V_s - L_{sh} C_{sh} \omega^2\right) \sin(\omega t) + R_{sh} C_{sh} V_s \omega \cos(\omega t)$  (7)

with initial values given in (8), shown at the bottom of the page, where *I*0 is the predefined line current for semiconductor switch operation.

Equation (7) is solved by MATLAB software, and its results are presented in Section V in detail. After damping transients, the fault current equation can be expressed by

$$iL = A \cos(\omega t) + B \sin(\omega t)$$

(9)

Where

$$\begin{split} A &= \frac{V_s \left[ R_{ab} C_{ab} \omega (d'-b'\omega^2) - (1-L_{ab} C_{ab} \omega^2) (c'\omega - a'\omega^3) \right]}{(c'\omega - a'\omega^3)^2 + (d'-b'\omega^2)^2} \\ B &= \frac{V_s \left[ R_{ab} C_{ab} \omega (a'\omega^3 - c'\omega) - (1-L_{ab} C_{ab} \omega^2) (d'-b'\omega^2) \right]}{(c'\omega - a'\omega^3)^2 + (d'-b'\omega^2)^2} \\ a' &= L_s L_{ab} C_{ab} \\ b' &= R_s L_{ab} C_{ab} + L_s R_{ab} C_{ab} + R_{ab} L_{ab} C_{ab} \\ c' &= L_s + R_{ab} C_{ab} R_s + L_{ab} \\ d' &= R_s L_{ab} C_{ab} R_s + L_{ab} \end{split}$$

By considering (9) and choosing proper values for *L*sh, *C*sh, and *R*sh, it is possible to limit the line current in the fault condition in a way that its value is near to the prefault line current. In this case, if the fault occurs, the PCC voltage will not sense the fault.

#### 4. Design Considerations

As discussed in Section II, Ldc is used to limit the increasing speed of the fault current and help the semiconductor switch to turn off in a safe condition.

Therefore, its value can be chosen by considering the current characteristics of the semiconductor switch.

Fig. 5 Design considerations

For resonant circuit design, two main cases should be taken into account: The first one is equating the resonance part equivalent impedance with the load impedance; the second is the generated heat in the resistor of the resonance part during fault and its design problem.

The equivalent impedance of the resonance part Zeq can be derived as follows:

$$Z_{eq} = R_{sh} - j \omega C_{sh} j\omega L_{sh} = L_{sh} C_{sh}R_{sh} + j\omega L_{sh}.$$

(11)

For equating this impedance with the load impedance, Lsh should be equal to the load inductance. The corresponding capacitor value Csh can be calculated considering the resonance condition between it and Lsh. Finally, the resistor value should be chosen in a way that Lsh/CshRsh is equal to the load resistance. However, it is difficult to equate these impedances exactly, and it is an ideal case because of load variation on distribution feeders. From a practical point of view, the parameters of the resonance part can be determined by using the history of measurements of the load at protected feeder and discussed calculations.

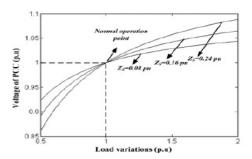

The following discussion deals with the operation of the proposed structure in practical condition. Fig. 5 shows the magnitude of the voltage deviation of the PCC of the test system from its base value (which is the prefault voltage magnitude of the PCC). The horizontal axis in this figure shows the magnitude of the impedance of the load in per unit where the base value is its impedance of the ideal case. The dashed line shows the existence of the ideal case. The parameter in this figure is the magnitude of the source impedance. This figure shows that, for a wide range of load magnitude variations (0.5–2 p.u. with fixed resonance part parameters), the voltage magnitude of the

PCC for postfault condition changes in an acceptable range, particularly for low values of |Zs|.

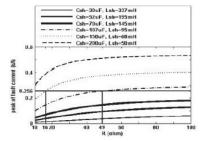

Fig. 6. Variation of the fault current magnitude with respect to Rsh.

For considering the generated heat in the resistance of the resonance part, it is possible to change the values of Lsh, Csh, and Rsh and decrease the real part of (11). Note that the magnitude of Zeq should be kept constant. Fig. 6 shows the fault current magnitude with respect to Rsh. The parameter in this figure is resonant LC. The lower limit of Rsh is selected to ensure proper transient response of the resonant circuit. The standard values for Csh are obtained from [33], and Lsh is calculated by considering the resonance condition between it and Csh in power frequency. As a numerical example, it is considered that the feeder's average current is 256 A. In this condition, the predesired value of the fault current (256 A) can be achieved by two values for resonant circuit parameters as follows.

Case 1)  $C \sinh = 150 \,\mu\text{F}$ ,  $L \sinh = 68 \,\text{mH}$ , and  $R \sinh = 16 \,\Omega$ . Case 2)  $C \sinh = 107 \,\mu\text{F}$ ,  $L \sinh = 95 \,\text{mH}$ , and  $R \sinh = 49 \,\Omega$ . |Z eq|'s in cases 1 and 2 are equal. However, in case 2, the real part of Z eq is smaller than its value in case 1. Therefore, the generated heat in  $R \sinh$  is reduced in fault condition. As a result, the design of  $R \sinh$  becomes simpler from a thermal point of view.

### 5. Simulation Results

The power circuit topology in Fig. 3 is used for simulation in the fault condition. The simulation parameters are shown in

Table I. The fault starts at 1 s and continues to 1.12 s (six cycles of power frequency).

| Source Side Data | Power source                                                          | 20 kV, 50Hz,<br>$Z_{sauce} = 0.57 + j \omega 0.003\Omega$                               |

|------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                  | Transformer                                                           | 20 kV/6.6 kV, 10 MVA, 0.1 p.u.                                                          |

| FCL Data         | dc side                                                               | $L_{ok} = 0.01 \text{ H},$<br>$V_{DP} = 3V, V_{SW} = 3V, 1_0 = 0.5\text{k/s}$           |

|                  | Resonance<br>part                                                     | $L_{sk} = 0.068 \text{ H}_{*} \text{ C}_{sh} = 150 \mu\text{F}$<br>$R_{sk} = 16 \Omega$ |

| Load Side Data   | $Z_{line} = 0.5\Omega_{\perp}Z_{2col} = 15 + fa0.1\Omega_{\parallel}$ |                                                                                         |

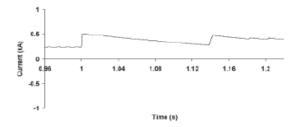

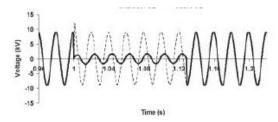

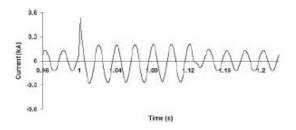

The simulation results for the line current are shown in Fig. 7.

Note that the current scales of the figures are selected different to show more details. As the fault occurs, without using FCL, the fault current increases extremely and has asymmetrical nature.

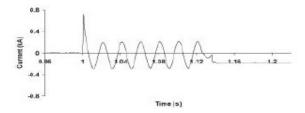

[Fig. 7(a)]. Also, without using Rsh in the resonant circuit, transient oscillations appear on the line current caused by LC resonance, as shown in Fig. 7(b). After damping of Fig. 7. Fault current iL(t). (a) Without FCL. (b) Without Rsh in the resonance-type FCL. (c) With the proposed FCL.

When the fault current reaches to *I*0 that is the predefined fault level, the semiconductor switch turns off, and the line current is limited in the fault condition. After fault removal, the semiconductor switch turns on, and the line current returns to the normal state, after negligible distortion. Although the proposed FCL can limit the fault current, this current magnitude can vary according to Fig. 7(c). Therefore, it is necessary to set Fig. 10. PCC voltage of the A phase () without and () with the proposed FCL. the secondary switching device for full short-circuit current of the power system.

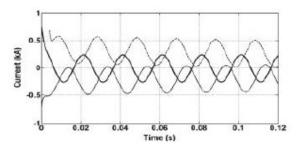

Fig. 8. DC reactor current idc(t) for the A phase.

Fig. 9. Resonance part current during the fault ish(t) for the A phase

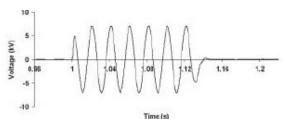

Fig. 10. PCC voltage of the A phase ( ) without and ( ) with the proposed FCL

Fig. 8 shows the dc reactor current. As the fault occurs, it starts to charge until semiconductor switch turning-off. After semiconductor switch turning-off, the freewheeling diode turns on and discharges Ldc. After fault removal, Ldc recharges because of resonant circuit voltage. By discharging the resonant circuit, the dc reactor current discharges and returns to the normal state.

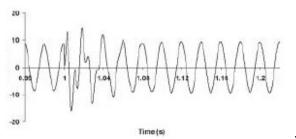

The current of the resonance part during the fault  $i\operatorname{sh}(t)$  for the A phase is shown in Fig. 9. It is obvious that, after semiconductor switch operation, the line current will be equal to the resonance part current. Fig. 10 shows the PCC voltage with and without using the proposed structure. As shown in this figure, the proposed FCL can prevent voltage sag on PCC properly. Also, the PCC voltage without using  $R\operatorname{sh}$  in the proposed FCL is shown in Fig. 11. It is observed that undesired distortions appear on the PCC voltage caused by the resonance current. The capacitor voltage is shown in Fig. 12.

To demonstrate the accuracy of the calculations, differential equation (7) that shows the line current during fault is solved by MATLAB software, and its result is shown in Fig. 13. This figure is in good agreement with

Fig. 7(c). The peak value of the current in both figures [Figs. 7(c) and 13] is 256 A.

Fig. 11. PCC voltage of the A phase without using *R*sh in the proposed FCL.

Fig. 12. Capacitor voltage VC(t) for the A phase.

Fig. 13. Calculated fault current iL(t) by MATLAB software

The values and variation of the curve show that the results of the calculations are adapted by the simulation result of the PSCAD/EMTDC software. This can prove the correction of (7)–(10). To study the nonideal case which is discussed in Section IV, the load is changed to 0.5 p.u. in the simulation system, and its results are shown in Figs. 14 and 15.

Fig. 14 shows the line current (A phase) for the nonideal case.

As shown in this figure, the line current is smaller than its value during fault. The PCC voltage in such condition is shown in Fig. 15. According to this figure, small voltage sag appears in PCC. This voltage sag is predictable considering Fig. 5.

To determine the rating of the FCL components, it is possible to use the simulation results as well as the design considerations mentioned in Section IV. Of course, for all semiconductor devices, the maximum ON-state current is the peak of the line current. The maximum OFF-state voltage for these devices is the PCC voltage during the fault. The current rating of Ldc is the peak of the line current. Also, the resonance part inductance Lsh will appear during the fault. Therefore, in the worst condition, its voltage will be the PCC voltage. Thus, its current rating can be determined.

Fig. 15 The PCC voltage

For the capacitor *C*sh, a simple voltage-dividing method can be used between it and the resistor *R*sh.

#### 6. Experimental Setup

The performance of the proposed FCL is experimentally investigated using a laboratory-scale power system simulator. The power system for the experimental study is shown in Fig. 3. Note that the control circuit of the proposed FCL is implemented by software. The experimental setup parameters and the control circuit data are presented in Table II. According to the available element values in the market and experimental setup facilities, the component values in the experimental setup are selected as much as possible near to the simulation

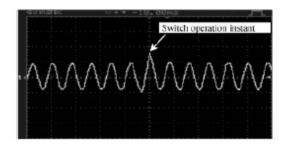

values which were obtained by the proposed design procedure. Fig. 16 shows the line current by using the proposed FCL. This figure is in good agreement with Fig. 7(c). The resonance part current during fault is shown in Fig. 17.

Fig. 16. Line current by using the proposed FCL (current/div.: 5 A; time/div.:25 ms).

Fig. 17. Current of the resonance part during fault (current/div.: 5 A; time/div.:25 ms).

Fig. 18. PCC voltage without using the FCL (voltage/div.: 50 V; time/div.: 25 ms).

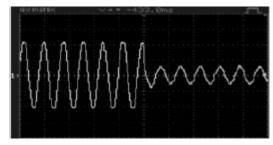

The PCC voltage without using the proposed FCL is shown in Fig. 18. It is observed that the PCC voltage drops strongly.

Using the proposed FCL prevents this voltage sag, as shown in Fig. 19. In such condition, a negligible distortion appears on the PCC voltage at the fault occurrence instant. Notice that the time scale in Fig. 19 is magnified to emphasize the small distortion of the voltage in the fault instant. Figs. 18 and 19 are in accordance with Fig. 10. Fig. 20 shows the capacitor voltage in the fault condition. It is in agreement with Fig. 12.

#### 7. Conclusion

In this paper, a new topology of parallel-LC-resonancetype FCL that includes a series resistor with the capacitor of the LC circuit has been introduced. The analytical analysis and design considerations for this structure have been presented. The overall operation of the mentioned FCL in normal and fault conditions has been studied in detail. Also, the simulation and experimental results have been involved to validate the analytic analyses. All previously proposed FCLs have good Fig. 19. PCC voltage by the proposed FCL (voltage/div.: 50 V; time/div.: 10 ms). Fig. 20. Capacitor voltage during fault (voltage/div.: 50 V; time/div.: 25 ms). current-limiting characteristics. However, as shown in this paper, the proposed structure can improve the power quality of the distribution system in addition to fault current limiting. The proposed resonance-type FCL can limit the fault current in a way that the PCC voltage does not face considerable sag during fault. This means that, in case of transient faults, it is not necessary to open the line by a circuit breaker. By using Rsh in the proposed topology, the transient state after fault damps quickly. In addition, it is capable of controlling the fault current at constant value that is not possible in common seriesresonance-type FCLs.

#### References

- [1] M. Jafari, S. B. Naderi, M. Tarafdar Hagh, M. Abapour, and S. H. Hosseini, "Voltage sag compensation of point of common coupling (PCC) using fault current limiter," *IEEE Trans. Power Del.*, vol. 26, no. 4, pp. 2638–2646, Oct. 2011.

- [2] S. P. Valsan and K. S. Swarup, "High-speed fault classification in power lines: Theory and FPGA-based implementation," *IEEE Trans. Ind. Electron.*, vol. 56, no. 5, pp. 1793–1800, May 2009.

- [3] P. Rodriguez, A. V. Timbus, R. Teodorescu, M. Liserre, and F. Blaabjerg, "Flexible active power control of distributed power generation systems during grid faults," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2583–2592, Oct. 2007.

- [4] M. F. Firuzabad, F. Aminifar, and I. Rahmati, "Reliability study of HV substations equipped with the fault current limiter," *IEEE Trans. Power Del.*, vol. 27, no. 2, pp. 610–617, Apr. 2012.

- [5] A. Y. Wu and Y. Yin, "Fault-current limiter applications in medium- and high-voltage power distribution systems," *IEEE Trans. Ind. Electron.*, vol. 34, no. 1, pp. 236–242, Jan./Feb. 1998.

- [6] M. Tarafdar Hagh and M. Abapour, "Non-superconducting fault current limiters," Euro. Trans. Power Electron., vol. 19, no. 5, pp. 669–682, Jul. 2009.

- [7] M. Tarafdar Hagh, M. Jafari, and S. B. Naderi, "Transient stability improvement using non-superconducting fault current limiter," in *Proc. IEEE 1st Power Electron. Drive Syst. Technol. Conf.*, Feb. 2010,pp. 367–370.

- [8] S. H. Hosseini, M. Tarafdar Hagh, M. Jafari, S. B. Naderi, and S. Gassemzadeh, "Power quality improvement using a new structure of fault current limiter," in *Proc. I EEE ECTI\_CON*, May 2010, pp. 641– 645

- [9] S.-H. Lim, H.-S. Choi, D.-C. Chung, Y.-H. Jeong, Y.-H. Han, T.-H. Sung, and B.-S. Han, "Fault current limiting characteristics of resistive type SFCL using a transformer," *I EEE Trans. Appl. Supercond.*, vol. 15, no. 2, pp. 2055–2058, Jun. 2005.

- [10] B. C. Sung, D. K. Park, J. W. Park, and T. K. Ko, "Study on a series resistive SFCL to improve power system transient stability: Modeling, simulation and experimental verification," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2412–2419, Jul. 2009.

- [11] M. Abapour and M. Tarafdar Hagh, "Non-superconducting fault current limiter with controlling the magnitudes of fault currents," *IEEE Trans. Power Electron.*, vol. 24, no. 3, pp. 613–619, Mar. 2009.

- [12] H.-S. Choi, N.-Y. Lee, Y.-H. Han, T.-H. Sung, and B.-S. Han, "The characteristic analysis between flux-coupling and flux-lock type SFCL according to variations of turn ratios," *I EEE Trans. Appl. Supercond.*, vol. 18, no. 2, pp. 737–740, Jun. 2008.

- [13] M. T. Hagh, S. B. Naderi, and M. Jafari, "New resonance type fault current limiter," in *Proc. IEEE Int. Conf. PECon*, Nov./Dec. 2010, pp. 507–511.

- [14] K. Arai, H. Tanaka, and M. Inaba, "Test of resonancetype superconducting fault current limiter," *IEEE Trans. Appl. Supercond.*, vol. 16, no. 2, pp. 650–653, Jun. 2006.

- [15] H. Arai, M. Inaba, and T. Ishigohka, "Fundamental characteristics of superconducting fault current limiter using LC resonance circuit," *IEEE Trans. Appl.* Supercond., vol. 16, no. 2, pp. 642–645, Jun. 2006.

- [16] H. G. Sarmiento, "A fault current limiter based on an LC resonant circuit: Design, scale model and prototype field tests," in *Proc. iREP Symp. Bulk Power Syst. Dyn. Control-VII, Revitalizing Oper. Rel.*, Aug. 2007, pp. 1–5.

- [17] S. Henry and T. Baldwin, "Improvement of power quality by means of fault current limitation," in *Proc. 36th Southeastern Symp. Syst. Theory*, Sep. 2004, pp. 280–284.

- [18] C. Meyer and R. W. De Doncker, "LCC analysis of different resonant circuits and solid-state circuit breakers for medium-voltage grids," *IEEE rans. Power Del.*, vol. 21, no. 3, pp. 1414–1420, Jul. 2006.

- [19] Z. Li, M. Li, Z. Zhou, C. Zhou, D. Du, H. Liu, R. Zhan, and Z. Zhan, "Research on dynamic simulation of the resonance fault current limiter," in *Proc. Int. Conf. Power Syst. Technol.*, Oct. 2010, pp. 1–6.

- [20] The MathWorks, Inc., LN: 161051 MATLAB version 7.6.0.324 (R2008a), Feb. 2008 LN: 161051.

- [21] Manitoba HVDC Research Centre, LN: 684003 Licensed for University of Tabriz, LN: 684003.

- [22] M. Tarafdar Hagh and M. Abapour, "DC reactor type transformer inrush current limiter," *IET Elect. Power Appl.*, vol. 1, no. 5, pp. 808–814, Sep. 2007.

- [23] Globalspec, Inc., The Engineering Search Engine. [Online]. Available: http://www.globalspec.com

- [24] B. Abdi, A. H. Ranjbar, G. B. Gharehpetian, and J. Milimonfared, "Reliability considerations for parallel performance of semiconductor switches in high-power switching power supplies," *I EEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2133–2139, Jun. 2009.

- [25] X. He, A. Chen, H. Wu, Y. Deng, and R. Zhao, "Simple passive lossless snubber for high-power multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 53, no. 3, pp. 727–735, Jun. 2006.

- [26] L. Zarri, M. Mengoni, A. Tani, G. Serra, and D. Casadei, "Minimization of the power losses in IGBT multiphase inverters with carrier-based pulsewidth modulation," *I EEE Trans. Ind. Electron.*, vol. 57, no. 11,pp. 3695–3706, Nov. 2010.

- [27] J. Bauman and M. Kazerani, "A novel capacitor-switched regenerative snubber for DC/DC boost converters," *I EEE Trans. Ind. Electron.*, vol. 58, no. 2, pp. 514–523, Feb. 2011.

- [28] M. R. Amini and H. Farzanehfard, "Three-phase soft-switching inverter with minimum components," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2258–2264, Jun. 2011.

- [29] General Atomics, Electronics Systems, High Voltage Capacitors and Power Supplies. [Online]. Available: http://www.ga-esi.com/EP